玄铁C910

时间:2025-12-30

点击:101

收藏

简介

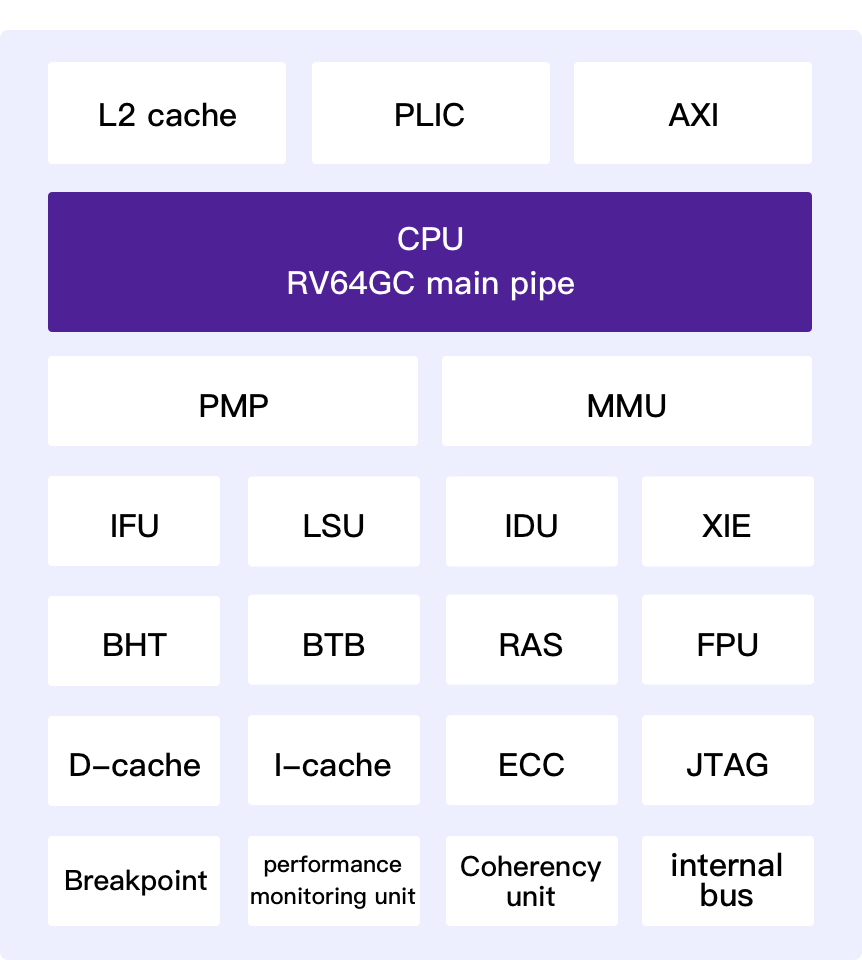

玄铁C910是一款兼容RISC-V架构的64位超高性能处理器,凭借在架构和微架构方面的创新,带来业界领先的计算性能和频率。 C910支持硬件数据一致性,支持AXI4主接口和设备一致性接口,采用Sv39虚拟地址系统,搭配玄铁内存属性扩展(XMAE)技术。另外,包含标准CLINT和PLIC中断控制器,支持RV兼容的调试接口和性能监测单元。 采用12级多发乱序流水线,典型工作频率>2.5GHz,是首款实现规模化量产的高性能乱序RISC-V处理器。采用3发射、8执行的深度乱序执行架构,针对算术运算、内存访问以及多核同步等方面进行了增强。 主要应用于对通用性能要求较高的高性能消费终端、边缘计算等领域。

特性

规格说明

| 特性 | 描述 |

|---|---|

| 架构 | RV64GC |

| SMP | 同构多核,每个Cluster最多4核 |

| 流水线 | 12级 |

| 玄铁扩展 | 玄铁指令扩展(XIE) |

| 玄铁内存属性扩展(XMAE) | |

| 浮点单元 | 支持单精度浮点 |

| 支持 RISC-V F、D 指令扩展 | |

| 支持IEEE 754-2008标准 | |

| 接口总数 | AXI4-128主接口 |

| 设备一致性接口 | AXI4-128从接口 |

| 指令Cache | 32KB/64KB可选,可选奇偶校验 |

| 数据Cache | 32KB/64KB可选,可选ECC |

| L2 Cache | 256KB~8MB可选,可选ECC |

| MMU | Sv39内存管理 |

| PMP | 0-16个保护区可选 |

| 中断控制器 | 可配置的平台级中断控制器(PLIC) |

| Dhrystone | 5.8 DMIPS/MHz(O2) |

| CoreMark | 6.96 CoreMark/MHz(O3) |

结构图表