芯来 UX1000 系列(20、30、40、60)

UX1000系列有三种不同的配置分类:UX1020,UX1030,UX1040和UX1060。UX1020是2译码宽度的处理器,拥有平衡的性能和面积功耗;UX1030是3译码宽度的处理器,拥有较好的性能和较低的面积功耗;UX1040是4译码宽度的处理器,拥有较高的性能以及优秀的面积功耗;UX1060是6译码宽度的处理器,拥有更高性能,主要面对高性能应用领域。

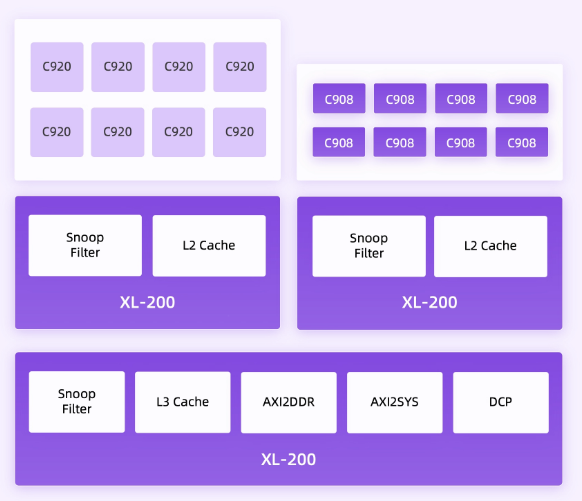

XL-200是一款支持多核多Cluster的互联IP,提供最大支持单簇8核(一级级联)和多簇32核(二级级联)的处理器扩展方案,能够有效降低多Cluster系统互联数据传输所需带宽、软件编程难度,减少额外的Cache访问并优化系统功耗。 主要应用于具有多核多簇互联需求的、有高并发算力要求的领域。

| 特性 | 说明 |

|---|---|

| Cluster接口 | 采用AMBA4 ACE协议 |

| 一级级联最多支持单簇8核,二级级联最多支持8簇32核 | |

| 同步/异步可选 | |

| 原生支持C920/C908/C908X/R908处理器 | |

| 设备一致性接口Device Coherency Port(DCP) | 采用ACE4-Lite DVM(兼容AXI4)协议 |

| DCP数量0-7个可选 | |

| 位宽128/256 bit可选 | |

| 性能监测单元 | 包含6组性能计数器用于性能检测 |

| 一级级联 L2 Cache 二级级联 L2/L3 Cache | 0/1MB/2MB/3MB/4MB/6MB/8MB可选 |

| 采用16路组相连,特殊大小采用12路组相连 | |

| 与上级Cache采用动态包含性关系 | |

| 支持ECC校验 | |

| 最多支持4 Slice并行访问 | |

| 可配置Tag/Data访问延迟周期数 | |

| 支持软件动态开关,支持二级级联L3 Cache | |

| 支持Retention | |

| Snoop Filter | 512K/1M/2MB/3MB/4MB/6MB/8MB/16MB/32MB可选 |

| 支持MESI一致性协议 | |

| 支持ECC校验 | |

| 主设备接口 | 一级级联支持AXI4(兼容AXI3)/ACE协议,二级级联支持AXI4(兼容AXI3)协议 |

| 位宽128/256-bit可选 | |

| 接口数量1-4个可选 | |

| 低延时外设接口Low Latency Port(LLP) | 采用AXI4(兼容AXI3)协议 |

| 位宽128-bit |